Energy-Efficient Computing Architectures

Common project-team with INRIA Rennes – Bretagne Atlantique, IRISA, CNRS, ENS Rennes, University of Rennes 1

Cairn is located on two campuses: Rennes and Lannion

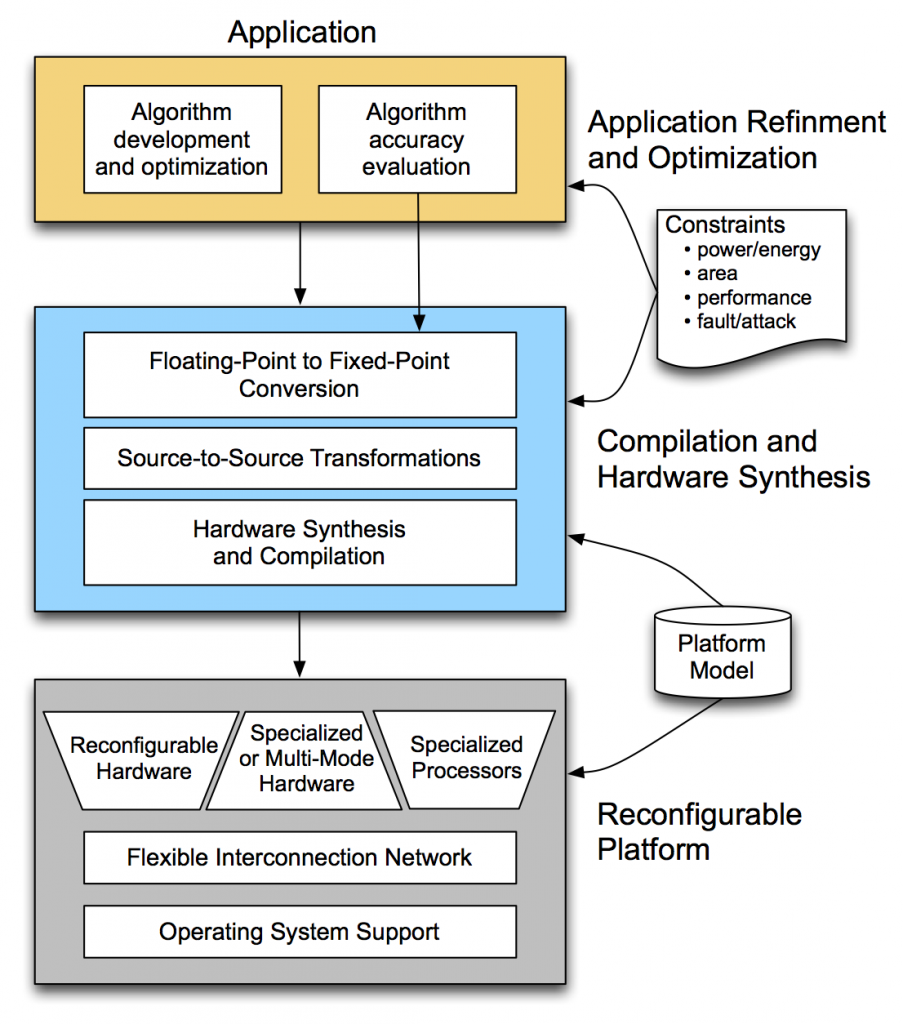

Abstract: The CAIRN project-team researches new architectures, algorithms and design methods for flexible, secure, fault-tolerant, and energy-efficient domain-specific computing architectures. Due to the performance and energy-efficiency requirements of system-on-chip (SOC), it becomes difficult to rely only on programmable processor solutions. To address this issue, we promote/advocate the use of reconfigurable hardware accelerators, which can offer higher performance at a lower energy cost, while preserving a high level of flexibility. The team studies these systems from three angles: (i) The design of new accelerator architectures with a focus on energy efficiency and fault tolerance. (ii) The development of their corresponding design flows (compilation and synthesis tools) to enable their automatic design from high-level specifications. (iii) Efficient management of different components in heterogeneous platforms.

The team has been created on January the 1st, 2008 and is a “reconfiguration” of the former R2D2 research team.

The development of complex applications is traditionally split into three stages: a theoretical study of the algorithms, an analysis of the target architecture, and the implementation. When facing new emerging applications such as high-performance, low-power and low-cost mobile communication systems or smart sensor-based systems, it is mandatory to strengthen the design flow by a joint study of both algorithmic and architectural issues. Cairn’s design flow is organized in levels which refer to our three research themes: application optimization (new algorithms, fixed-point arithmetic and advanced representations of numbers), architecture optimization (reconfigurable and specialized hardware, application-specific processors), and stepwise refinement and code generation (code transformations, hardware synthesis, compilation).

Keywords: Hardware Accelerators, Compiling, Embedded Systems, Energy Consumption, Parallelism, Wireless Sensor Networks, Security, Signal Processing, Reconfigurable Hardware, Computer Arithmetic, System-On-Chip