### Inria Sophia-Antipolis & Rocquencourt

#### with University of Nice-Sophia/CNRS UMR I3S

Robert de Simone

Our main objective

# FORMAL MODEL-DRIVEN ENGINEERING FOR OPTIMIZED ALLOCATION OF EMBEDDED APPLICATIONS ONTO MODERN ARCHITECTURES

### Motivations

#### Small-scale execution platforms become increasingly parallel

- From HPC clusters and data-centers,

- From graphics and embedded processors

- From networks processors

- ... To the mainstream current user of smartphones, tablets, notebooks

- Applications deal increasingly with external physical environment

- From avionics and automotive

- From mobile phone platforms

- From robotics

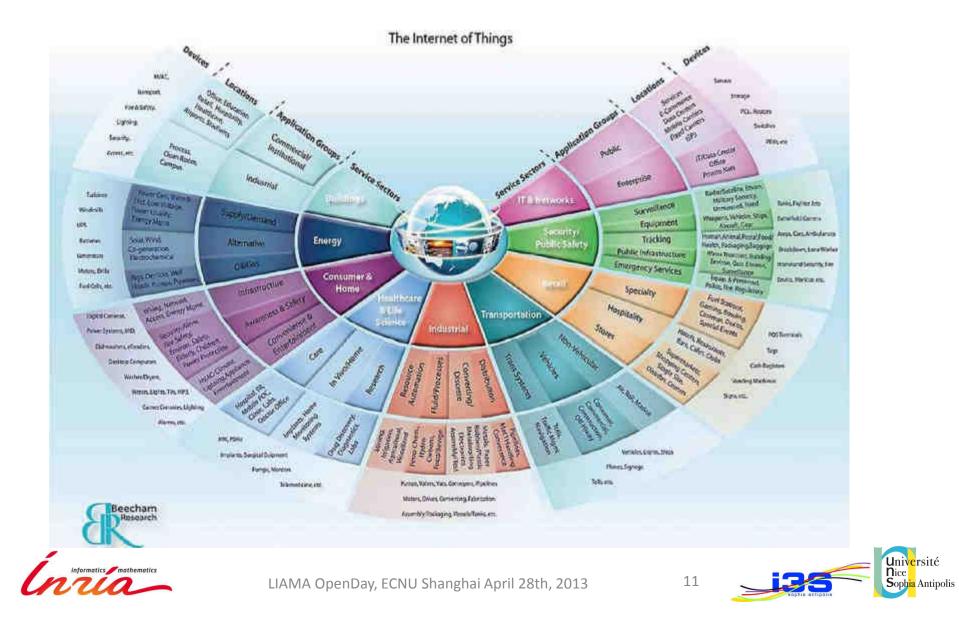

... To general Cyber-Physical systems and Internet of things

### Motivations

#### Small-scale execution platforms become increasingly parallel

- From HPC clusters and data-centers,

- From graphics and embedded processors

- From networks processors

- ... To the mainstream current user of smartphones, tablets, notebooks

- Applications deal increasingly with external physical environment

- From avionics and automotive

- From mobile phone platforms

- From robotics

- ... To general Cyber-Physical systems and Internet of things

Use of formal models and methods to provide recipes for better mapping (allocation + scheduling) ?

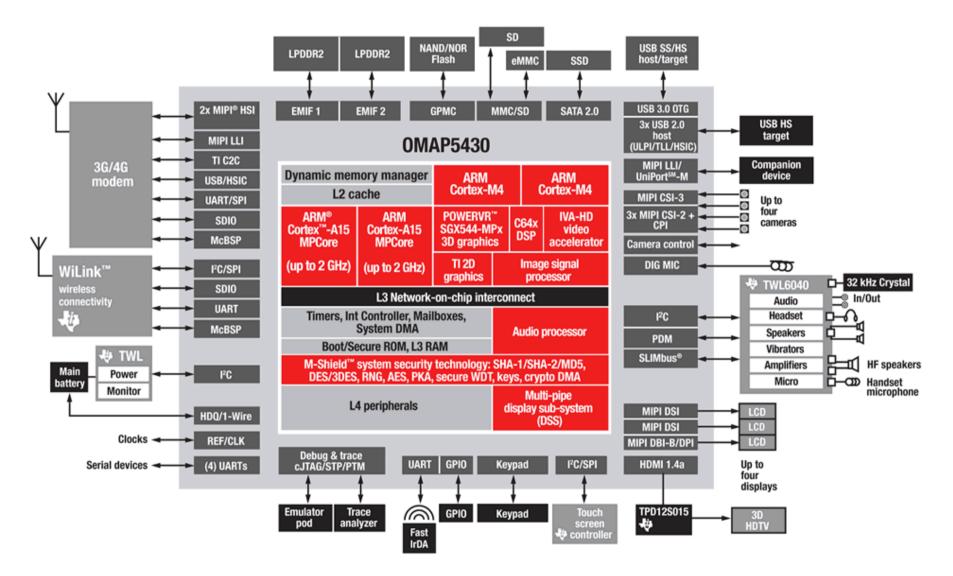

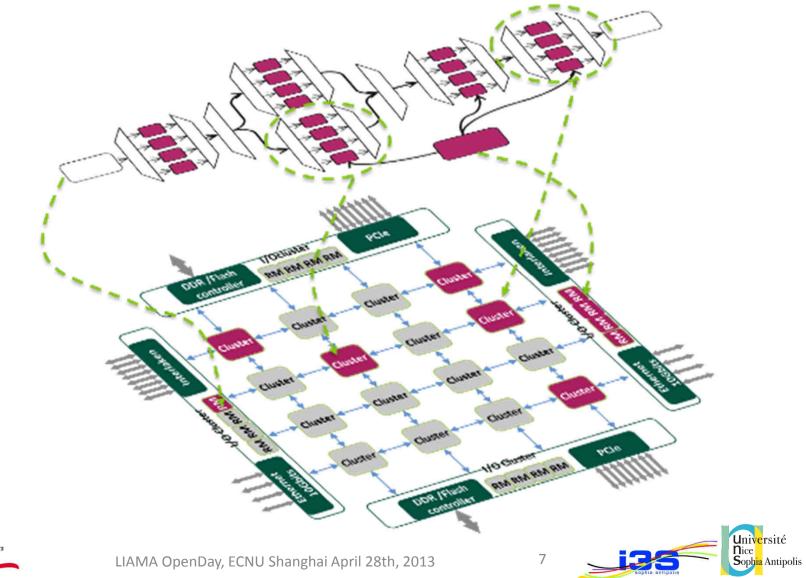

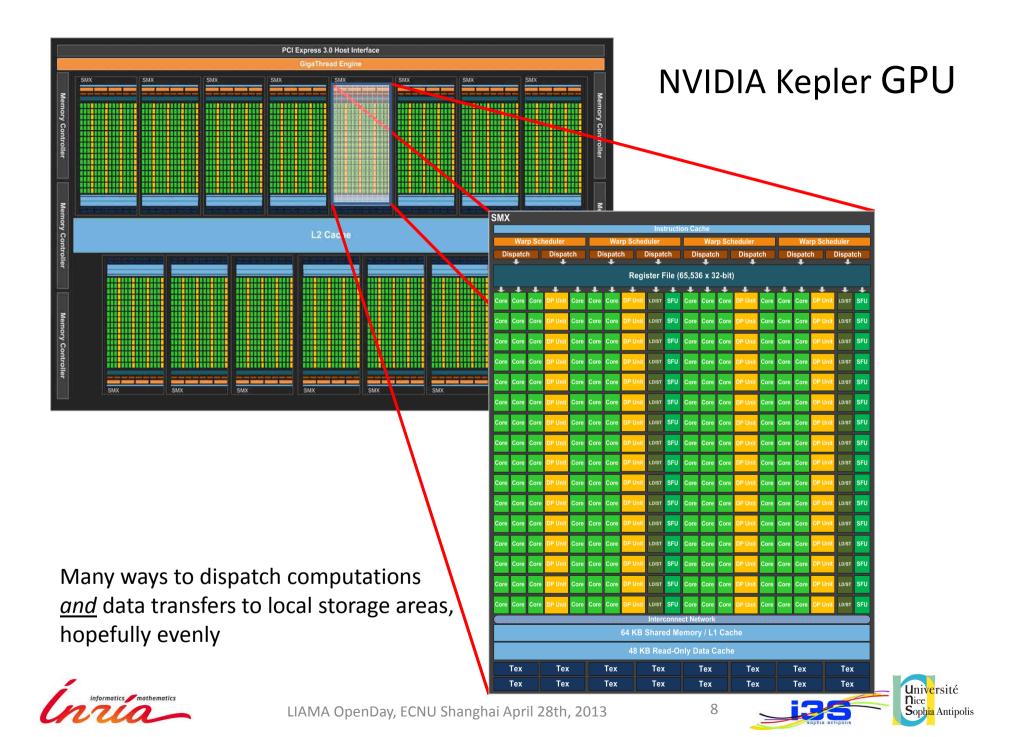

Homogeneous or heterogeneous parallel execution platforms Embedded platforms Mobile phone virtual platforms Automotive/avionics local networks Sensor networks Massively Parallel Processor Arrays (from HPC and Cloud Computing) Manycore systems-on-chip (with on-chip networks) Kalray MPPA 256, SThorM (was PF 2012), Tilera, Cavium, Intel... Hardware Accelerators **GP-GPU** hybrid architectures (from graphics processing) Witnessing convergence between embedded, HPC, and *PC/phone/tablet architectures*

# **MODERN** <u>A</u>RCHITECTURES

.

### TI OMAP5430 SoC

### Kalray MPPA-256

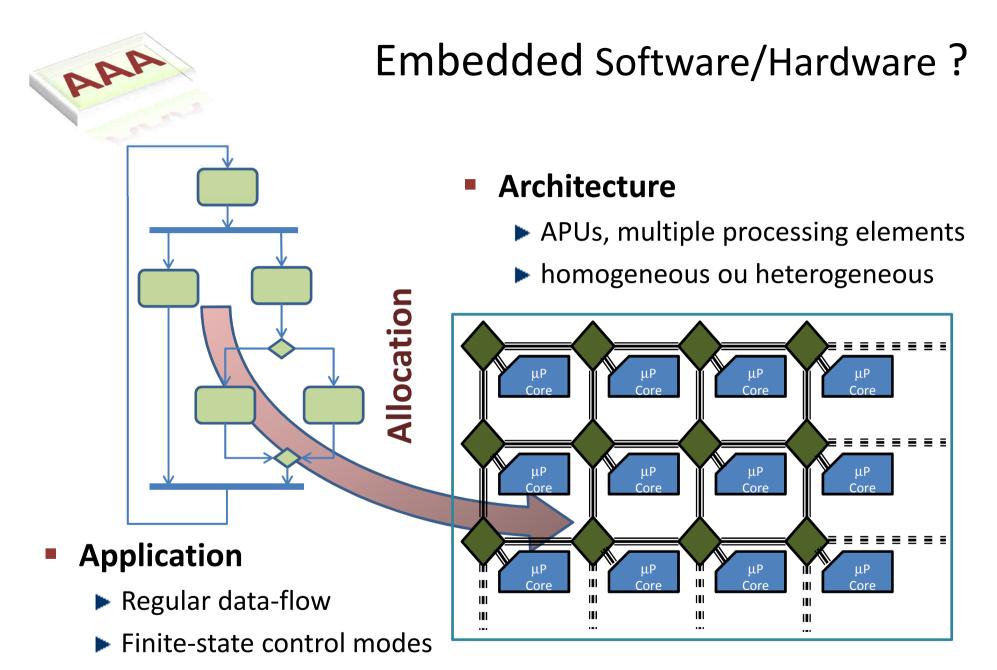

#### Dataflow streaming applications, with control of the environment

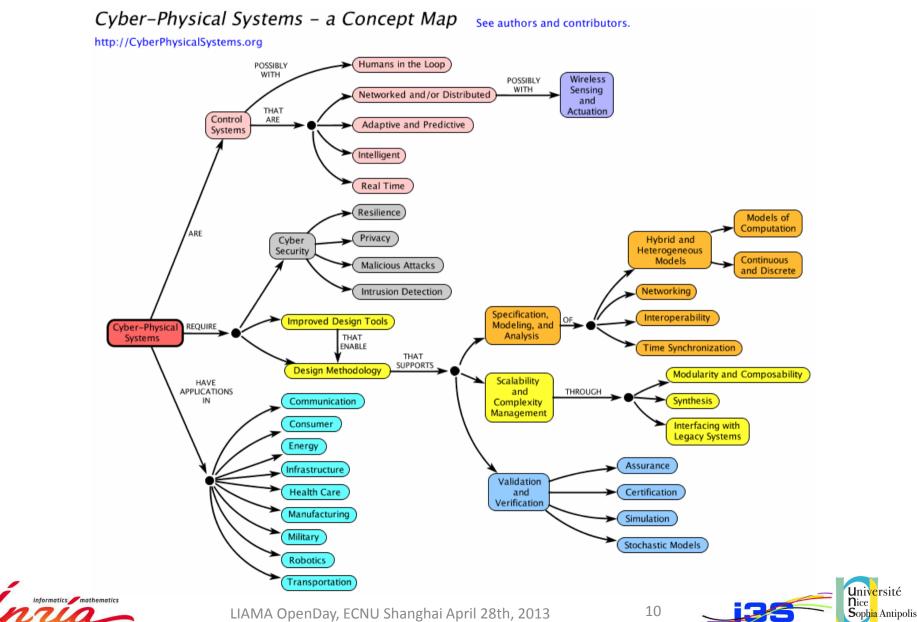

#### Cyber-Physical Systems domain

Strong interactions with physical environment, interfaces In our case mobile phones, automotive, avionic domains

$\rightarrow$  Esterel, SCADE, ...

Multimedia signal/image processing

- → Nested Loops with affine bounds (static control) parallel compilation

- Dataflow process networks (Kahn, Petri, many variants)

# Concurrency important (task-level, data-level parallelism) EMBEDDED APPLICATIONS

Abstract descriptions as Models of Computations

# CyberPhysical domain

# Internet of Things span

### Compilation **no longer automatic** on fancy parallel platform

Issues:

Mapping/distribution (spatial) of functions/tasks onto resources Scheduling (temporal) to share resources across several application functions

Become as important on data communications & memory transfers as on computations

# **OPTIMIZED** <u>A</u>LLOCATION

→ Careful modeling of interconnect, timing aspects

### Need for mathematical properties to support analysis

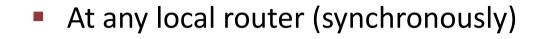

Dataflow PNs, Synchronous languages, Nested loops w/ static bounds are <u>both</u>

- ✓ executable languages <u>and</u>

- ✓ formal Models of Computation and Communication (MoCCs),

with rich theory for analysis

### Optimization techniques to best fit applications to architectures FORMAL MODEL-DRIVEN ENGINEERING

#### Theoretical results on static regular scheduling and routing

- **KRG** model with k-periodic routing/switching words

- Latency-Insensitive Design in SoC modeling

- Smooth schedules and even data distributions (mechanical/Christofffel words)

→ K-Passa tool

- Full axiomatisation for network topology transformations

. . .

### All2All diffusion routing schemes (cellular automata)

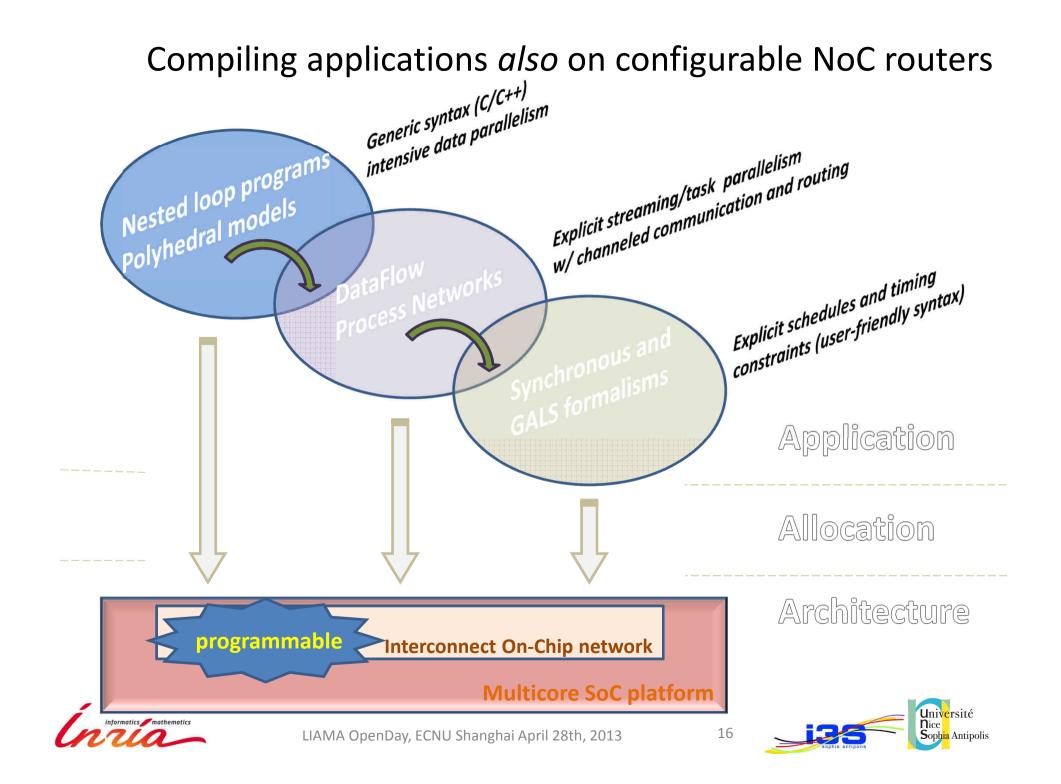

### Engineering such a design flow

We use **MDE environments** and tools to represent application, platform and allocation models

#### $\rightarrow$ OMG UML profile MARTE

The resulting framework also allows abstract application modeling to tune target hardware design

Platform-based design

# FORMAL MODEL-DRIVEN ENGINEERING

#### MARTE Time model:

- Multiple logical clocks (signals), multiform time

- **CCSL** (Clock Constraint Specification Language) to assert timing requirements in a formal setting, as integral part of the model

- Translation to formal models (variants of Buchi automata) for schedulability

- **TimeSquare** simulation environment

- Many formal connections with existing formalisms:

#### AADL, AutoSar/TADL, Spin/Promela, UppAal, nu-SMV,...

LIAMA OpenDay, ECNU Shanghai April 28th, 2013

# Thank you for attention !

**Questions ?**